随着中国“芯”计划的确立,国家出台了各项政策扶持国内的半导体产业发展,第三代半导体的研制,国产化十新基建,引爆芯片强劲需求,展示芯片很强动力和潜力。半导体芯片的生产环境及设备的要求是极高的,就半导体芯片洁净区的环境要求有哪些?

半导体芯片生产环境的要求

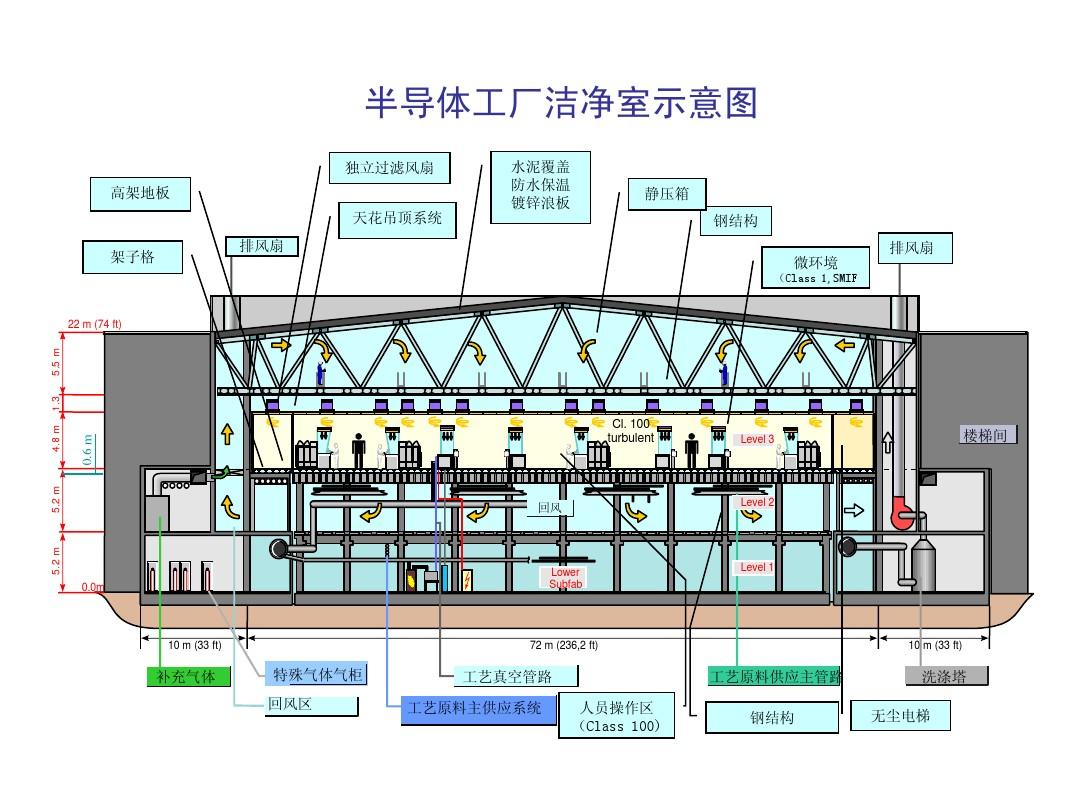

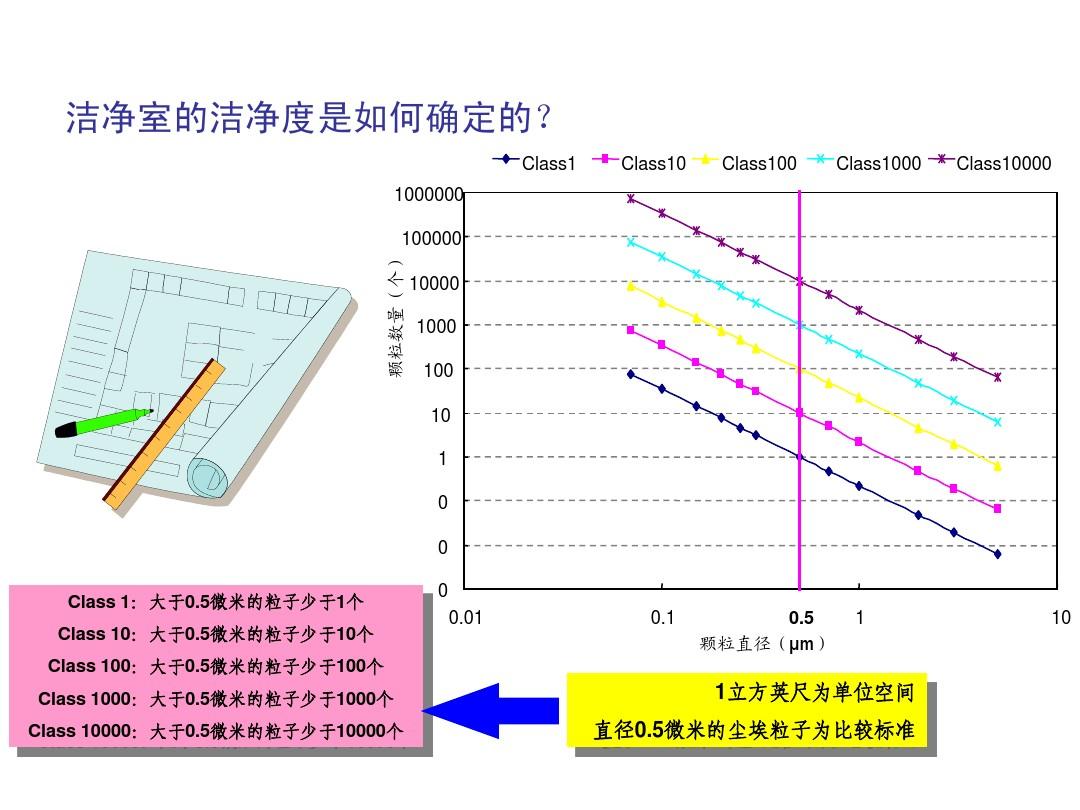

由于电子产品在制造、生产过程中对室内空气环境和品质的要求极为严格,主要以控制微粒和浮尘为主要对象,同时还对其环境的温湿度、新鲜空气量、噪声等作出了严格的规定。

1、室内的噪声级(空态):不应大于65dB(A)

2、垂直流洁净室满布比不应小于60%,水平单向流洁净室不应小于40%,否则就是局部单向流了。

3、与室外的静压差不应小于10Pa,不同空气洁净度的洁净区与非洁净区之间的静压差不应小于5Pa。

4、洁净室内的新鲜空气量应取下列二项中的最大值:

5、补偿室内排风量和保持室内正压值所需的新鲜空气量之和。

6、保证供给洁净室内每人每小时的新鲜空气量不小于40m3。

7、净化空调系统加热器,应设置新风,超温断电保护,若采用点加湿时应设置无水保护,寒冷地区,新风系统应设置防冻保护措施。无尘室的送风量。

复杂设计施工与高建造费用

电子芯片洁净车间有着严格的洁净度要求,可想而知,其设计施工也是相当复杂的。此外,洁净度越高,建造费用也越高。例如100级(FS 209)单向流洁净室,仅室内装修与空调洁净系统的建造费用为10000元/㎡。再加上消防、三废、供配电和自控系统,建造费用更是高达25000元-30000元/㎡。

当完成电子芯片洁净车间的建造后,还要经过3方面的验收,即:空态验收、静态验收、动态验收,只有完成验收才能投入日常使用。因此,面临巨大的技术风险,以及后续运行、维护和调试、检测的压力。

半导体芯片温湿度控制

半导体(FAB)洁净室中相对湿度的目标值大约控制在30至50%的范围内,允许误差在±1%的狭窄的范围内,例如光刻区──或者在远紫外线处理(DUV)区甚至更小──而在其他地方则可以放松到±5%的范围内。

因为相对湿度有一系列可能使洁净室总体表现下降的因素,其中包括:

● 细菌生长;

● 工作人员感到室温舒适的范围;

● 出现静电荷;

● 金属腐蚀;

● 水汽冷凝;

● 光刻的退化;

● 吸水性。

细菌和其他生物污染(霉菌,病毒,真菌,螨虫)在相对湿度超过60%的环境中可以活跃地繁殖。一些菌群在相对湿度超过30%时就可以增长。在相对湿度处于40%至60%的范围之间时,可以使细菌的影响以及呼吸道感染降至最低。

相对湿度在40%至60%的范围同样也是人类感觉舒适的适度范围。湿度过高会使人觉得气闷,而湿度低于30%则会让人感觉干燥,皮肤皲裂,呼吸道不适以及情感上的不快。

高湿度实际上减小了洁净室表面的静电荷积累──这是人们希望的结果。较低的湿度比较适合电荷的积累并成为潜在的具有破坏性的静电释放源。当相对湿度超过50%时,静电荷开始迅速消散,但是当相对湿度小于30%时,它们可以在绝缘体或者未接地的表面上持续存在很长一段时间。

相对湿度在35%到40%之间可以作为一个令人满意的折中,半导体洁净室一般都使用额外的控制装置以限制静电荷的积累。

很多化学反应的速度,包括腐蚀过程,将随着相对湿度的增高而加快。所有暴露在洁净室周围空气中的表面都很快地被覆盖上至少一层单分子层的水。当这些表面是由可以与水反应的薄金属涂层组成时,高湿度可以使反应加速。幸运的是,一些金属,例如铝,可以与水形成一层保护型的氧化物,并阻止进一步的氧化反应;但另一种情况是,例如氧化铜,是不具有保护能力的,因此,在高湿度的环境中,铜制表面更容易受到腐蚀。

此外,在高的相对湿度环境下,由于水分的吸收,使烘烤循环后光刻胶膨胀加重。光刻胶附着力同样也可以受到较高的相对湿度的负面影响;较低的相对湿度(约30%)使光刻胶附着更加容易,甚至不需要聚合改性剂。

在半导体洁净室中控制相对湿度不是随意的。但是,随着时间的变化,最好回顾一下常见的被普遍接受的实践的原因和基础。

洁净室行业壁垒高,下游客户要求极其严格。IC 半导体、光电类产品制造商一次性建厂投资较高,其生产条件要求非常严格,任何一个小瑕疵会影响芯片和面板的良率,对洁净室的稳定性要求非常高。